# HOSTESS HOSTESS

Developer's Toolkit for the Hostess® i Series

St. Paul, Minnesota 55113 (612) 631-7654

Copyright © 1995. Comtrol Corporation All Rights Reserved. First Edition March 1, 1995

### Trademarks

The Comtrol logo is a registered trademark of Control Systems, Inc. Hostess is a registered trademark of Comtrol Corporation.

Comtrol is a trademark of Comtrol Corporation.

80286 is a trademark of Intel Corporation.

Borland and Turbo Debugger are registered trademarks of Borland International, Inc.

IBM PC is a trademark of International Business Machines Corporation.

Intel is a registered trademark of Intel Corporation.

Microsoft and MS-DOS are registered trademarks of Microsoft Corporation.

Windows is a trademark of Microsoft Corporation.

UNIX is a registered trademark of UNIX System Laboratories (USL).

Product names mentioned herein may be trademarks and/or registered trademarks of their respective companies.

Comtrol Corporation Document Number: 6254 Printed in the U. S. A.

## Before You Begin

#### Scope

IN.

This guide describes the functionality of the Hostess i controller, along with information needed to program the controller.

This manual provides information for Hostess i controllers with a serial number of HI07-002409 or greater.

The EPROM on the controller changed for models HI07-002409 or greater to reflect a revision to the Borland® Turbo Debugger® (version 4.02). This means if you use this manual for earlier serial numbers of the controller:

Li

區

- You will find that the steps for using the Turbo Debugger are not quite correct.

- You can not use the 4.02 or greater version of the Turbo Debugger with the EPROM on the controller; you must use version 3.2 or lower.

L

匾

Note: Unfortunately, Borland International did not make the 4.02 version of the Turbo Debugger backward compatible with previous levels.

### Prerequisites

Lin.

Lii.

This manual assumes that have also ordered the Development Board Option (discussed below). To effectively use this toolkit, the manual assumes the following conditions exist:

- The controller is installed in your system.

- If it is not installed, refer to the User 's Guide for this information.

- Your ISA personal computer system consists of the following:

- DOS version 4.01 or higher

- Optionally, Windows™ 3.1 or higher running in 386-enhanced mode

- You are running one of the following compilers on the development system:

Ji.

Lil

II.

Uil.

- Borland C++ (version 4.02 or later)

- Microsoft® Visual C++ (version 1.0 or later)

Lit.

Note: For a detailed list of the requirements for the development system, refer to the documentation for the compiler.

#### Audience

This guide is primarily for the programmer who is familiar with C language or 80286<sup>TM</sup> Assembly language.

# What the Developer's Toolkit Contains

The Developer's Toolkit consists of the following pieces:

- This manual.

- A Developer's Toolkit diskette containing sample programs for your controller.

- The Advanced Micro Devices manual for the serial communications controller on your controller.

To readily use the Toolkit, you should have ordered the *Development Board Option* on your controller. This option is provided at no additional charge and includes the following pieces:

- A debug/reset header soldered to the controller

- A debug/reset box and cable

Note: If you have any questions regarding the Toolkit or the Development Board Option, contact Comtrol using the information provided in Appendix A.

### Organization

This guide contains the following information:

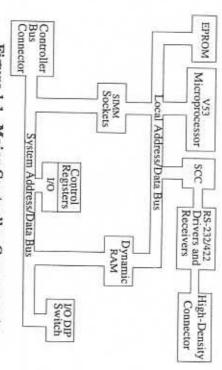

Section 1. Controller Overview

Describes features and components of the controller.

Section 2. Sample Programs

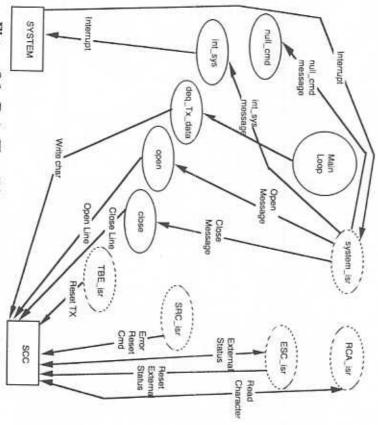

Discusses the toolkit's sample programs for the controller.

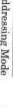

Section 3. System I/O Addresses

Discusses setting I/O addresses and the control registers.

Section 4. Controller Internal I/O Addresses

Discusses controller internal I/O addresses and the configuration control register.

Section 5. Dual-Port Memory

Discusses how dual-port memory is mapped.

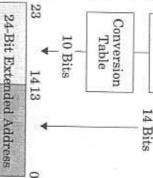

Section 6. Extended Addressing Mode

Describes relocating addresses and expanding memory.

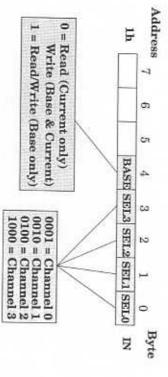

Section 7. Direct Memory Access

Discusses the Direct Memory Access Control Unit (DMAU) registers.

Section 8. Interrupts

Explains how interrupts affect the system processor and the controller. Section 9. Timers

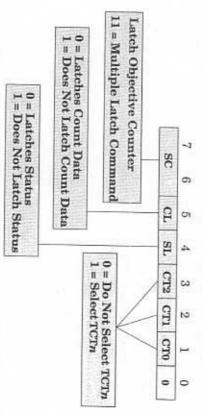

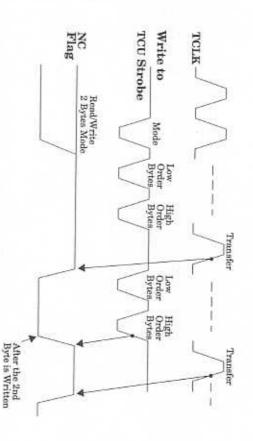

Describes the Timer Control Unit (TCU) and its registers. The Count and Multiple Latch commands are also discussed

and Multiple Latch commands are also discussed.

Section 10. SCC Port Communication

通

لقا

Lists the command and data register I/O addresses.

Section 11. Downloading and Executing a Control Program

Discusses the steps involved to download and avenue a control

Discusses the steps involved to download and execute a control program.

Section 12. Debugging Tools

Discusses the following debugging tools:

- DPMMAP.C

- Status flag groups (SFGs)

- Trace Buffer

The Borland

Li

- The Borland Turbo Debugger

- Firmware debugger

直

Appendix A. Developer's License Agreement and Contacting Comtrol

Provides you with a copy of the Developer's License agreement and lists methods for contacting Comtrol for technical support.

Index

E.

Bibliography

Am8530H/Am85C30 Serial Communications Controller 1992 Technical Manual. U.S.A. Advanced Micro Devices, Inc., 1992. NEC 16-Bit V-Series Microprocessor Data Book. U.S.A: NEC Electronics Inc., May 1990.

## **Table of Contents**

| 3.7.4. Control Register #3                             |      |

|--------------------------------------------------------|------|

| ***************************************                |      |

| Control Desired #1                                     |      |

| Control Degister #1                                    |      |

| 3.7.1 Writing Control Bonistons                        |      |

| Control Register Oversiew                              | 30.0 |

|                                                        | 000  |

| Interminting the Controller                            | 2    |

| Resetting and Initializing the Controller              | 3.4. |

| Reading the Controller Identification Byte             | 3.3  |

| Setting System I/O Addresses                           | 3.2. |

|                                                        | 3.1. |

| tion 3. System I/O Addresses                           | Sec  |

| Program                                                |      |

|                                                        |      |

| Utility                                                |      |

| . Compiling the Sample Programs Using the Borland Make | 2.7. |

| 2.6.1. Invoking HITERM2-18                             | 1    |

| HITERM.C2-                                             | 2.6  |

| HILIB.C                                                | 0.0  |

| THE CONDERSON                                          | 10   |

| DPLOADERC                                              | 24   |

| Dual-Port RAM Configuration for CPC RIN                | 2.3  |

|                                                        | 2.2  |

|                                                        | 2.1  |

| ction 2. Developer's Toolkit Sample Programs           | Seci |

| . Toolkit                                              | 1.2  |

| 1.1.3.                                                 |      |

| DEROM                                                  |      |

| EDDON                                                  |      |

| 1 1 1 Microprocessor                                   |      |

| oller Features                                         | 1.1  |

| Section 1. Controller Overview                         | Sec  |

| Tablesxv                                               | Ta   |

| rlowchartsxiii                                         | 110  |

| riguresxii                                             | 118  |

| Examplesx1                                             | i X  |

| Die of Contents                                        | BI   |

|                                                        | 3    |

| Bibliography                                           | Bil  |

| ranizationiv                                           | Or   |

| What the Developer's Toolkit Containsiv                | W.   |

|                                                        | Au   |

| ites                                                   | Pr   |

| ***************************************                | Sco  |

| ou Begin                                               | Be   |

|                                                        | 1    |

⊴.

Section 8. Interrupts

8.1. Interrupting the Sy

8.2. Interrupting the Co

8.3. Internal Interrupt S

8.4. Interrupt Vectors...

8.5. Interrupt Mask Reg

8.6. SCC Interrupt Vecto

8.7. Initializing SCC Inte

7.2.3. 7.2.4. 7.2.6. 7.2.7. 7.2.8.

Section 9. Timers

TCU Operation Procedure.....

Initializing SCC Interrupt Vectors ..... SCC Interrupt Vector Types..... Interrupt Mask Register (IMR)..... Interrupt Vectors..... Internal Interrupt Service Routine......

| i.   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | la.  | 2.1. TMD (Timer Mode Register) 9-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Ĭ.   | n    | ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| L    | - Mi | n 9. Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| U    | 1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Lil. | T    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Lii. | A.   | ternal Interrupt Service Routine8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| li   | _T   | ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1 1  |      | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| i.   | n    | DMD (Mode Control Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| i    | Ì    | DDC (Device Control Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| U    | 1    | 2.4. DBA/DCA (Base/Current Count Register) 7.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| يال  | T    | 7.2.2.2. DCH Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |      | 7-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| UiL  | 'n   | E :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1    | . !  | 7.2.1 DICM (Initialize Command Document)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ii.  | Fi.  | OMA Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| L    |      | 7 Direct Manager Assessment Addressing Mode6-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| U    | n.   | Addressing Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| li.  | m    | 3.2.1. Page Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1    | 1    | ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Ĭ.   | A.   | ided Addressing Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| L.   | F    | Ū                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Ú    | 1    | Overview5-1 Dual-Port Memory Man                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1    | M    | ğ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| L    | _1   | - Configuration Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| U    | Li   | 4.3.4.1. Int 24h — Configuration Control Regis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1    | L    | Configuration Control Boriston Tetransia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | H    | 4.3.2. DTR Source 4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| d    | j    | Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Configuration Control Register 4.3 1 RS 232 and RS 433 Control Register 4.3 1 RS 232 and RS 433 Control Register 4.3 1 RS 232 and RS 433 Control Register 4.3 1 RS 232 and RS 433 Control Register 4.3 1 RS 232 and RS 433 Control Register 4.3 1 RS 232 and RS 433 Control Register 4.3 1 RS 232 and RS 433 Control Register 4.3 1 RS 232 and RS 433 Control Register 4.3 1 RS 232 and RS 433 Control REGISTER 4.3 1 RS 232 and RS 433 Control REGISTER 4.3 1 RS 232 and RS 433 Control REGISTER 4.3 1 RS 232 and RS 433 Control REGISTER 4.3 1 RS 232 and RS 433 Control REGISTER 4.3 1 RS 232 and |

|      |      | The state of the s |

7.2.1.

6.3.

4.2. 4.3.

4.3.1. 4.3.2. 4.3.3.

Section 4. Controller I/O Addresses

3.7.5.

Overview....

Control Register #4.....

.3-13

4

Controller Internal I/O Addresses ......4-1

| Index | A.1.<br>A.2.                                             | App                                                                 | 12.4.   |                                                    | 12.3. |                                    |                                                                                                                                            | 12.1.                          | 11.3. |      | Sect.<br>11.1.<br>11.2.                                                                                 | 10.1<br>10.2                                                                     | 9.5.         | 9.3.             |                  |

|-------|----------------------------------------------------------|---------------------------------------------------------------------|---------|----------------------------------------------------|-------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------|------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------|------------------|------------------|

|       | Developer's License Agreement A-1 Contacting Comtrol A-2 | Appendix A. Developer's License Agreement and Contacting<br>Comtrol | Table 1 | 12.3.2. Firmware Debugger Command Definitions 12.8 | - 200 | 12.2.4. Invoking the Remote Kernel | 12-2.1. Setting Up the Hardware Environment 12-1<br>12-2.2. Connecting a Two-PC Environment 12-2<br>12-2.3. Configuring Symbol Tables 12-3 | 12.1. Debugging Tools Overview |       |      | Section 11.Downloading and Executing a Control Program 11.1 Overview 11.2 Using Firmware Utilities 11.2 | Section 10.SCC Port Communications 10.1. Command and Data Register I/O Addresses | Using Timers | Multip<br>9.4.1. | 9.2.2.<br>9.2.3. |

|       | 2 i                                                      |                                                                     | F       | י בי מ                                             | 1000  | ώ 4 α                              | చనగ                                                                                                                                        | <u>-</u> -                     | 4     | ယ်ယံ | 2 i                                                                                                     | 51                                                                               | 110          | 99               | 5                |

# List of Examples, Figures, Flowcharts

### Examples

### Figures

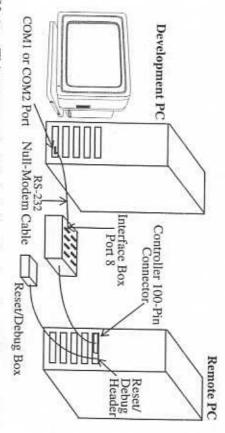

| ystem and the    | Figure 12-1.Cabling between the Development System and Remote System                             |

|------------------|--------------------------------------------------------------------------------------------------|

| 9-8              | Figure 9-6. NC Flag Change                                                                       |

| 9-7              | Figure 9-5. TST Format                                                                           |

| 9-6              | Figure 9-4. Multiple Latch Command Format                                                        |

| 9-6              | Figure 9-3. Count Latch Command Format                                                           |

| 9-4              | Figure 9-2. TCKS Register                                                                        |

| 9-2              | Figure 9-1. TMD Register                                                                         |

| 7-12             | Figure 7-9. DMK Register                                                                         |

| 7-12             | Figure 7-8. DST Register                                                                         |

| 7-10             | Figure 7-7. DMD Register                                                                         |

| 7-9              | Figure 7-6. DDC Register                                                                         |

| mat7-8           | Figure 7-5. DBA/DCA Read/Write Command Format.                                                   |

| ister7-7         | Figure 7-4. DBC/DCC Read/Write Command Register                                                  |

| 7-7              | Figure 7-3. DCH Register (Write)                                                                 |

| 7-6              | Figure 7-2. DCH Register (Read)                                                                  |

| 7-E              | Figure 7-1. DICM Register                                                                        |

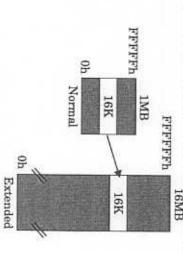

| 6-               | Figure 6-1. Expanding Memory                                                                     |

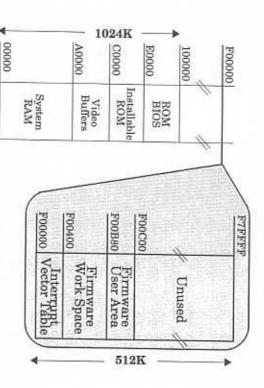

| 5-2              | Figure 5-2. Controller's View of Its RAM                                                         |

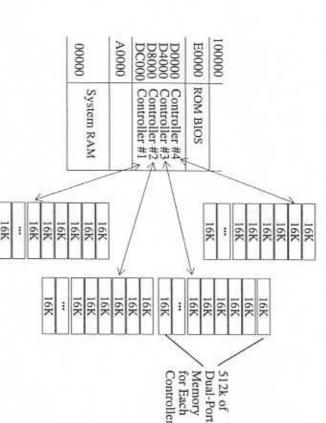

| d-Port RAM5-2    | Figure 5-1. System View of the Controller's Dual-Port RAM.                                       |

| One Megabyte3-1; | Figure 3-1. Four Controllers Addressed Under One                                                 |

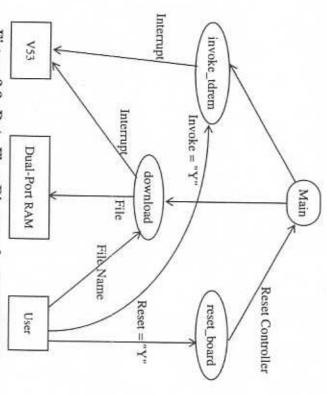

| rogram2-<br>C2-1 | Figure 2-1. Data Flow Diagram for the CPC.C Program Figure 2-2. Data Flow Diagram for DPLOADER.C |

| 1-               | Figure 1-1. Major Controller Components Figure 1-2. Installing the Toolkit                       |

### Flowcharts